As the FPGA gaming market continues to evolve, we're witnessing an interesting dynamic play out among developers, hobbyists, and commercial entities. The MiSTer project, once a trailblazer in retro gaming on FPGA hardware, now finds…

Schematic Modeling & The Role of Schematics in…

https://youtu.be/35jaodbqmV4

About Investigating, Interpreting & Resolving Timing issues in…

https://youtu.be/4JdadPbIOuM

Midway Z and Y Unit FPGA/ Core Overview

https://youtu.be/LnATOKkrSEo

Creating a CPU: The Data Approach (1)

Creating a CPU can be a very daunting task for someone. There's a lot of functionality embedded all in a single chip, and not to mention the pinout and interfaces that chip has with other…

New Core Work: TMS34010, NARC & Smash TV

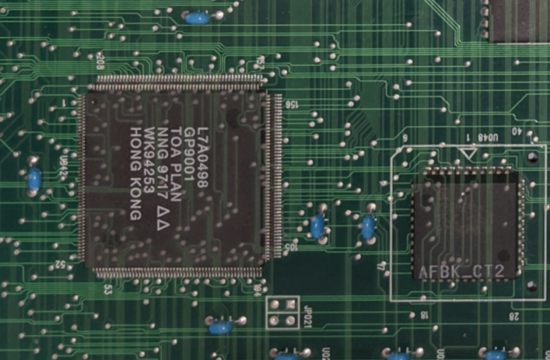

As of the past month or so, I have been putting together a core for 2 games: NARC and Smash TV. More specifically, I have been writing a CPU/GPU core for the TMS34010 processor. About…

FPGA Core Development Series: Part 5

Last time, we talked about the graphics subsystem and how graphics work in general in the FPGA core. You learned some techniques used to draw things on the screen, and how graphics work on a…

FPGA Core Development Series: Part 4

In the last post we talked about the CPU module and what it should accomplish, as well as some strategies to debug and put together the module. In this post, I will discuss the graphics…

FPGA Core Development Series: Part 3

In the last part, we talked about putting together a loader which ensures that the game rom data is made available to the MiSTer and FPGA for use in SDRAM. Today, I will show you…

FPGA Core Development Series: Part 2

In the last post we learned about how to start a core development effort, and the importance of sourcing the real board and/or schematics to construct the FPGA model. Today, I will take you through…